Now when the segments works we need to select the right digit to lit. MAME has a layout system where it is possible to create simple layouts from textual descriptions. We will create a small layout and show how to manipulate this from the driver. The BCD digit is defined like this:

Now when the segments works we need to select the right digit to lit. MAME has a layout system where it is possible to create simple layouts from textual descriptions. We will create a small layout and show how to manipulate this from the driver. The BCD digit is defined like this:<led7seg> <color blue="0.0" green="0.0" red="0.75"></color>

</led7seg>

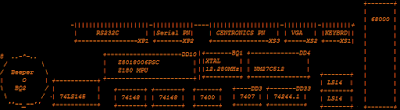

Which allows us to make it redish. The actual BCD display should look something like the picture to the right. To actually place out some digits we use the bezel<bezel element="digit" name="digit0">

<bounds bottom="885" left="70" right="100" top="840">

</bounds>

This defines "digit0" which can be manipulated from the driver by including the layout, or rather the compiled version which is compressed during build time.

We need to synchronize the update of the UI digit element with the ROM software so we know when to present the segments and to which digit. Fortunately there is an interrupt firing between the VIA shift register updates so we can create yes another trampoline in the driver code for this

MCFG_VIA6522_IRQ_HANDLER(WRITELINE(prodigy_state, irq_handler));

WRITE_LINE_MEMBER(prodigy_state::irq_handler)

{

m_maincpu->set_input_line(M6502_IRQ_LINE, state);

update_bcd();

}

We need also to know which digit to lit so we need to feed the 74145 from the VIA Port B bit 0 and 1. In fact Bit 2 and 3 are also connected but used for something else that we will explore later.

...

WRITE8_MEMBER( prodigy_state::via_pb_w )

{

m_74145->write( data & 0x0f ); // Write PB0-PB3 to the 74145

}

Viola, so when the interrupt fires the 74145 can be read to know the digit:

void prodigy_state::update_bcd()

{

LOGBCD("%s\n", FUNCNAME);

uint8_t ttl74145_data;

uint8_t digit_nbr = 4;

ttl74145_data = m_74145->read();

if ((ttl74145_data & 0x0f) != 0x00)

{

switch (ttl74145_data & 0x0f)

{

case 0x01: digit_nbr = 0; break;

case 0x02: digit_nbr = 1; break;

case 0x04: digit_nbr = 2; break;

case 0x08: digit_nbr = 3; break;

}

m_segments = m_digit;

output().set_digit_value( digit_nbr, m_segments);

}

}

The last statement will form the tag = "digit%c", '0' + digit_number; eg digit0 to digit3, and then lit the segments for that digit in the layout. Running the final code will render this in MAME:

Next step will be to trace out the keypad and get the software running, stay tuned!